(Knowledge for Development)

# KIBABII UNIVERSITY (KIBU)

MAIN CAMPUS

UNIVERSITY EXAMINATIONS

2021/2022 ACADEMIC YEAR

SPECIAL/SUPPLEMENTARY EXAMINATION

FIRST YEAR SECOND SEMESTER EXAMINATION

FOR THE DEGREE OF BACHELORS OF SCIENCE IN

(INFORMATION TECHNOLOGY)

**COURSE CODE:**

**BIT 124**

COURSE TITLE:

DIGITAL ELECTRONICS

DATE: 27/07/2022

TIME: 8.00 A.M. - 10.00 A.M.

2HRS

INSTRUCTIONS TO CANDIDATES:

ANSWER QUESTIONS ONE AND ANY OTHER TWO.

Paper Consists of 4 Printed Pages. Please Turn Over

#### QUESTION ONE [COMPULSORY] (30MARKS)

a) Distinguish between Multiplexers and demultiplexers

[1 mark]

b) Convert the binary number 1010 1011.011112 to;

i) Hexadecimal

[2 marks]

ii) Decimal

[2 marks]

c) Convert hexadecimal number A25C. 2A to;

i) Binary

[2 marks]

ii) Octal

[2 marks]

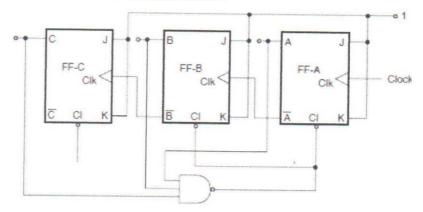

d) Refer to the counter schematic shown in the figure below.

i) Sketch the wave forms for the output of the flipflops

[3 marks]

ii) Determine the count sequence of this counter

[2 marks]

e) Determine SOP expression from the Karnaugh map shown below

[3 marks]

|                            | CD | CD | CD | CD |

|----------------------------|----|----|----|----|

| $\overline{A}\overline{B}$ | 1  | 1  |    | 1  |

| ĀΒ                         |    | 1  |    |    |

| AB                         |    |    |    |    |

| ΑB                         | 1  | 1  |    | 1  |

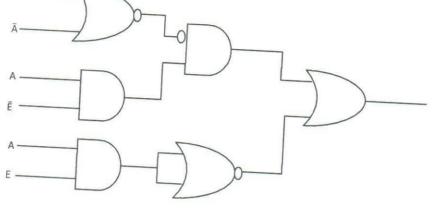

Determine the Boolean expression from the logic circuit shown below

Simplify the following Boolean function obtained in (f) above to a minimum number of literals

[3 marks]

[3 marks]

h) Obtain a truth table for the minimized logic circuit in 1(g) above

[3 marks]

Explain the application of magnitude comparator

[4 marks]

## **QUESTION TWO (20 MARKS)**

a) Describe the operation of a decoder

[6 marks]

b) Using a logic circuit, illustrate how a comparator is used in testing of equality

[4 marks]

c) Explain the operation of half- adder circuit as an arithmetic circuit

[6 marks]

d) Using relevant circuit diagram demonstrate synchronous parallel transfer of data from three bit register to another using J-K flip flops.

[4 marks]

# **QUESTION THREE (20 MARKS)**

a) Design a digital logic circuit to produce a 50 Hz output signal from an input signal of 3.2 KHz.

b) With the help of clocked JK flip flops and waveforms, explain the working of a MOD-8 down counter

c) List any three applications of de-multiplexers

[5 marks] [3 marks]

d) Explain the operation of a decoder circuit

[4 marks]

e) Explain how a decoder is used in the following areas

i) Computer memory

[2 marks]

ii) Input/Output device addressing

[2 marks]

### **QUESTION FOUR (20 MARKS)**

- a) A water tank feeds three separate processes. When any two of the processes are in operation at the same time, a signal is required to start a pump to maintain the head of water in the tank. Devise a logic circuit using nor-gates only to give the required signal.

- b) Describe any two applications of de-multiplexers

[4 marks]

[4 marks]

- c) Explain the following terms in relation to logic families;

- i) Power dissipation

[2 marks]

ii) Noise immunity

[2 marks]

d) Standardize the expression Y = (AB)' + A'BC + BC'

[4 marks]

e) Implement a truth table that satisfies the result in 4(d) above

[4 marks]

#### **QUESTION FIVE (20 MARKS)**

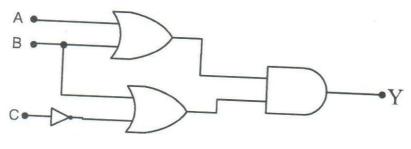

a) Derive a truth table for the circuit below.

[4 marks]

b) Describe the operation of flip flops in frequency division circuits

[6 marks]

c) Explain any three applications of decoder circuits

[6 marks]

d) Differentiate between multiplexers and de-multiplexers

[4 marks]